Ondřej Filip publikoval reportáž z ceremonie podpisu kořenové zóny DNS. Zhlédnout lze také jeho nedávnou přednášku Jak se podepisuje kořenová zóna Internetu v rámci cyklu Fyzikální čtvrtky FEL ČVUT.

Společnost BenQ uvádí na trh novou řadu monitorů RD určenou pro programátory. První z nich je RD240Q.

Byl aktualizován seznam 500 nejvýkonnějších superpočítačů na světě TOP500. Nejvýkonnějším superpočítačem nadále zůstává Frontier od HPE (Cray) s výkonem 1,206 exaFLOPS. Druhá Aurora má oproti loňsku přibližně dvojnásobný počet jader a dvojnásobný výkon: 1,012 exaFLOPS. Novým počítačem v první desítce je na 6. místě Alps. Novým českým počítačem v TOP500 je na 112. místě C24 ve Škoda Auto v Mladé Boleslavi. Ostravská Karolina, GPU

… více »GHC (Glasgow Haskell Compiler, Wikipedie), tj. překladač funkcionálního programovacího jazyka Haskell (Wikipedie), byl vydán ve verzi 9.10.1. Přehled novinek v poznámkách k vydání.

Po 9 týdnech vývoje od vydání Linuxu 6.8 oznámil Linus Torvalds vydání Linuxu 6.9. Přehled novinek a vylepšení na LWN.net: první a druhá polovina začleňovacího okna. Později také na Linux Kernel Newbies.

Byla vydána verze 0.2.0 v Rustu napsaného frameworku Pingora pro vytváření rychlých, spolehlivých a programovatelných síťových systémů. Společnost Cloudflare jej letos v únoru uvolnila pod licencí Apache 2.0.

Open source RDP (Remote Desktop Protocol) server xrdp (Wikipedie) byl vydán ve verzi 0.10.0. Z novinek je vypíchnuta podpora GFX (Graphic Pipeline Extension). Nová větev řeší také několik bezpečnostních chyb.

Rocky Linux byl vydán v nové stabilní verzi 9.4. Přehled novinek v poznámkách k vydání.

Dellu byla odcizena databáze zákazníků (jméno, adresa, seznam zakoupených produktů) [Customer Care, Bleeping Computer].

V lednu byl otevřen editor kódů Zed od autorů editoru Atom a Tree-sitter. Tenkrát běžel pouze na macOS. Byl napevno svázán s Metalem. Situace se ale postupně mění. V aktuálním příspěvku Kdy Zed na Linuxu? na blogu Zedu vývojáři popisují aktuální stav. Blíží se alfa verze.

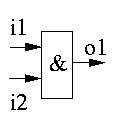

Nejdříve uvedeme základní pojmy. Z pohledu návrhu je procesor číslicový obvod. V číslicovém obvodu je třeba definovat dvě základní úrovně signálu - logická '0' a logická '1'. Číslicový obvod se skládá z hradel a propojení mezi nimi. Hradlo je elementární prvek, který realizuje základní funkci. Zde je příklad realizace logické funkce AND.

Hradlo na obrázku má dva vstupy a jeden výstup. Pokud je na obou vstupech '1', na výstupu hradla bude '1'. Při jakékoliv jiné kombinaci vstupů bude na výstupu '0'.

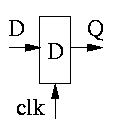

My budeme používat hradla realizující logické funkce AND, OR, NOT a XOR. S těmito hradly již můžeme vytvořit libovolnou logickou funkci. Něco nám ale pořád chybí - a to je paměťový prvek, který by pomohl vnést do našeho obvodu časovou závislost. Použijeme hradlo typu D, které si dokáže pamatovat hodnotu.

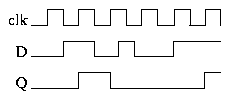

V okamžiku náběžné hrany (přechod z '0' do '1') hodinového signálu clk se na výstup Q zapíše hodnota vstupního signálu D, jinak zůstává hodnota na výstupu nezměněna. Na následujícím obrázku je znázorněn příklad časového průběhu, který demonstruje toto chování.

Hradlo D tedy funguje velmi jednoduše, ale, jak si ukážeme dále, spolu s pomocí logických hradel nám umožní navrhnout celý procesor.

Teď, když máme základní stavební prvky, můžeme začít navrhovat obvod. Ale jak? Existují návrhové systémy, kde graficky skládáme obvod z hradel a ta propojujeme. Pro složitější obvody je však tento přístup takřka vyloučen. Naštěstí existují jazyky, které nám umožní textově popsat strukturu obvodu. Jejich syntaxe je velmi podobná programovacím jazykům. V této podobnosti je ale skryto jedno velké nebezpečí - nemusíte si ani uvědomit, že popisujete hardware a nepíšete program. My budeme používat jazyk VHDL (VHSIC Hardware Description Language), který je u nás nejrozšířenějším jazykem pro návrh.

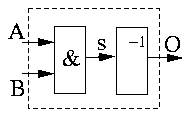

Základní prvky ve VHDL jsou entita a architektura. V deklaraci entity definujeme vstupy a výstupy obvodu, pomocí architektury tvoříme vlastní obvod. Dalším důležitým pojmem je signál, základní propojovací prvek. Signál si můžeme představit jako vodič, kterým spojujeme hradla. Vstupy a výstupy definované v entitě jsou také signály. Základem pro vytváření obvodu je příkaz přiřazení <=, který signálu na levé straně přiřadí hodnotu na pravé straně. Všechny uvedené pojmy si ukážeme na jednoduchém příkladu, realizaci obvodu na následujícím obrázku:

-- dve minuska jsou komentar

ENTITY jednoduchy_obvod IS -- entitu nazveme jednoduchy_obvod

PORT ( -- klicove slovo PORT

A, B: IN std_logic, -- dva vstupy, A a B (typ std_logic

-- znamena bezny vodic)

O: out std_logic -- jeden vystup

);

END jednoduchy_obvod; -- konec deklarace entity

ARCHITECTURE moje_architektura OF jednoduchy_obvod IS

-- tvorime obsah entity

signal s: std_logic; -- vytvorim si pomocny signal

BEGIN -- zacatek tela architektury

s <= A and B; -- v signalu s bude logicky soucin

-- signalu A a B

O <= not s; -- na vystupu O bude negace s;

END moje_architektura -- konec architektury

V deklaraci entity definujeme vstupy obvodu A a B a výstup O. Tím říkáme, jak bude vypadat obvod z vnějšku. Architekturu (tedy vnitřek obvodu) přiřadíme k entitě a v deklarační části si vytvoříme pomocné signály, v našem případě jediný signál s. V těle architektury (za klíčovým slovem begin) již píšeme schéma obvodu. V signálu s chceme mít logický součin signálů A a B. To implikuje vytvoření hradla AND. Na výstup O přiřazujeme negaci signálu s, což vede na vytvoření hradla NOT mezi signál s a výstup O.

Příště si ukážeme, jak vytvořit složitější obvody, a jakým programem si můžete VHDL kód odsimulovat na vašem PC.

Nástroje: Tisk bez diskuse

Tiskni

Sdílej:

![]()

![]()

![]()

![]()

![]()

![]()

! Jinak co že ses rozhodl psát na linuxový portál? Už se těším na pokračování, dojde i na ADL, ISDL a tato témata? A určitě také plz. popiš tu novou latch-like šílenost od Intelu, jsem líný si ji hledat.) tak určitě spíše na Model Sim. Jinak já osobně používám knihovny z FreeHDL, na testy vanilla CAD, sice z tabulek (zvlášť u složitého návrhu) by Luděk lezl po zdi

! Jinak co že ses rozhodl psát na linuxový portál? Už se těším na pokračování, dojde i na ADL, ISDL a tato témata? A určitě také plz. popiš tu novou latch-like šílenost od Intelu, jsem líný si ji hledat.) tak určitě spíše na Model Sim. Jinak já osobně používám knihovny z FreeHDL, na testy vanilla CAD, sice z tabulek (zvlášť u složitého návrhu) by Luděk lezl po zdi  , ale je tam dobře vidět distribuce signálu a rozepsané i to, co se děje ,,okamžitě`` což se někdy hodí. Docela mi vyhovuje Sonata. Ještě bych rád rozjel Alliance, zvláště ten její syntezátor a router mě zajímá, ale k tomu jsem se zatím ještě přes zaneprázdnosti v jiných oblastech nedostal. To mi tak připomíná, že bych mohl někdy do blogu zapsat sumarizaci letošního semestr a rozepsat návrh našeho miniprocesůrku (spíše chytřejšího XORu...), což za zablogování celkem stojí

, ale je tam dobře vidět distribuce signálu a rozepsané i to, co se děje ,,okamžitě`` což se někdy hodí. Docela mi vyhovuje Sonata. Ještě bych rád rozjel Alliance, zvláště ten její syntezátor a router mě zajímá, ale k tomu jsem se zatím ještě přes zaneprázdnosti v jiných oblastech nedostal. To mi tak připomíná, že bych mohl někdy do blogu zapsat sumarizaci letošního semestr a rozepsat návrh našeho miniprocesůrku (spíše chytřejšího XORu...), což za zablogování celkem stojí  .

. , clanek chci koncipovat jako uvod do VHDL, zaverem by mohl byt navrh casti nebo celeho procesoru ve VHDL. Hlavni duraz chci klast na klasicke rozdeleni registry-logika, takze "latch-like" procesor pri te prilezitosti zminim.

Taky diky vsem za zivou diskusi, i na jejim zaklade se muze vyvijet obsah dalsich dilu.

Za chvili mizim na tyden na dovolenou, tak pekne prazdniny!

, clanek chci koncipovat jako uvod do VHDL, zaverem by mohl byt navrh casti nebo celeho procesoru ve VHDL. Hlavni duraz chci klast na klasicke rozdeleni registry-logika, takze "latch-like" procesor pri te prilezitosti zminim.

Taky diky vsem za zivou diskusi, i na jejim zaklade se muze vyvijet obsah dalsich dilu.

Za chvili mizim na tyden na dovolenou, tak pekne prazdniny!

.

.~(a | b) == ~a & ~b;A naopak:

~(a & b) == ~a | ~b;A taky myslím, že s xorem to nijak nejde, ale nevím - o takové věci se moc nezajímám.

XOR netvoří úplný systém logických spojek (samotým XORem nelze realizovat např. negaci). Nicméně množina {XOR, T} (T je tautologie) již úplný systém logických spojek tvoří. T pak v praxi není nic jiného než logická "1", takže pomocí XORu lze zkonstruovat libovolný logický obvod.

.

.Jaj už jsem psal, množina {XOR, T} tvoří úplný systém logických spojek, takže pomocí těchto dvou operátorů opravdu lze složit libovolnou funkci. Úplných systémů logických spojek je celá řada, výjmečnost Shefferovy algebry (NAND) a Piercovy algebry (NOR) je pouze v tom, že zde je úplný systém logických spojek tvořen jednou jedinou spojkou.

P.S: "negativní tautologie" se většinou nazývá kontradikce

Tak jsem si to znovu rozmýšlel a obávám se, že nemáte pravdu. Položme

Af = f(0,0) ^ f(0,1) ^ f(1,0) ^ f(1,1)Pak elementárně A(f^g) = (Af) ^ (Ag) (XOR je komutativní a asociativní), ale problém je v tom, že pro všechny vaše stavební kameny (x,y,1) je Af rovno nule, takže vzhledem k výše uvedenému z nich nikdy nemáte šanci poskládat cokoli s Af = 1, např. AND. (Lidově řečeno: řekneme, že funkce je sudá, jestliže má v tabulce sudý počet jedniček. Snadno nahlédneme, že XOR dvou sudých funkcí je opět sudá funkce a protože funkce vracející první argument, funkce vracející druhý argument i tautologie jsou sudé funkce, nikdy z nich nesložíte lichou.)

Máte samozřejmě pravdu, úplný systém logických spojek tvoří až množina {XOR, T, AND či OR} (nebo jiná "větší" množina s XORem). Jdu si na studijní nechat zrušit zkoušku z matematické logiky...

Zjednodušeně řečeno to lze dokázat ve dvou krocích:

1. Nejprve musíte dokázat, že jakákoli logická funkce více proměnných lze napsat pomocí funkcí dvou proměnných a negace (funkce jedné proměnné). To samozřejmě dokázat lze, pro booleovské operace platí "běžná" pravidla, jako je asociativita, komutativita atd.

2. potom stačí pro vybranou funkci zjistit, zda pomocí ní lze realizovat všech šestnáct binárních funkcí dvou proměnných (s využitím výše zmíněných pravidel a de Morganova pravidla). To stačí pouze rozepsat na papíře a hned máte výsledek.