Richard Hughes oznámil, že službu Linux Vendor Firmware Service (LVFS) umožňující aktualizovat firmware zařízení na počítačích s Linuxem, nově sponzoruje také společnost HP.

O víkendu proběhla demopárty Outline 2026. Publikována byla prezentovaná dema. Upozornit lze na 16 bajtové, opravdu šestnáct bajtové, zvukově obrazové demo Wake Up! 16b (YouTube).

Byla vydána nová verze 9.5 multiplatformní digitální pracovní stanice pro práci s audiem (DAW) Ardour. Přehled novinek, vylepšení a oprav v poznámkách k vydání a na YouTube.

Dnes a zítra probíhá vývojářská konference Google I/O 2026. Sledovat lze na YouTube a na síti 𝕏 (#GoogleIO).

Canonical vydal Ubuntu Core 26. Vychází z Ubuntu 26.04 LTS a podporováno bude 15 let. Ubuntu Core je minimální neměnný operační systém určený pro vestavěné systémy.

Bylo vydáno OpenBSD 7.9. Po dlouhé době opět se songem: Diamond in the Rough.

Byl vydán Mozilla Firefox 151.0. Přehled novinek v poznámkách k vydání a poznámkách k vydání pro vývojáře. Řešeny jsou rovněž bezpečnostní chyby. Nový Firefox 151 bude brzy k dispozici také na Flathubu a Snapcraftu.

Elon Musk prohrál soudní spor se společností OpenAI, která se podle jeho žaloby odchýlila od původně uváděného cíle vyvíjet umělou inteligenci (AI) ku prospěchu lidstva. Porota včera po necelých dvou hodinách dospěla k jednomyslnému závěru, že Musk žalobu podal příliš pozdě. Musk byl jedním ze spoluzakladatelů společnosti OpenAI, která vznikla v roce 2015 a vyvinula populární chatovací systém ChatGPT. V roce 2018 na svůj post ve vedení

… více »Byla vydána nová verze 10.4 z Debianu vycházející linuxové distribuce DietPi pro (nejenom) jednodeskové počítače. Přehled novinek v poznámkách k vydání. Opraveny jsou zranitelnosti Copy Fail a Dirty Frag. Přibyl nový obraz pro Orange Pi 5B.

Pokud je zranitelnost Linuxu v nepoužívaném jaderném modulu, lze ji jednoduše vyřešit zakázáním automatického načítání tohoto konkrétního zranitelného modulu. Projekt ModuleJail si klade za cíl zvýšit bezpečnost Linuxu zakázáním automatického načítání všech nepoužívaných jaderných modulů. Jedná se o skript, který dá všechny nepoužívané jaderné moduly na blacklist (/etc/modprobe.d/modulejail-blacklist.conf).

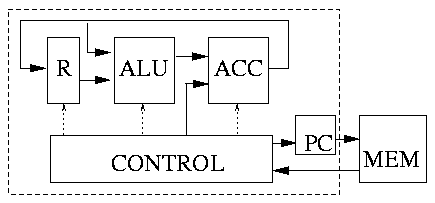

Pro naše ukázkové účely bude stačit úplně jednoduchá architektura procesoru, kterou vidíte na následujícím obrázku. Sběrnice jsou označeny plnou čarou, řídící signály jsou tečkované.

Vlastní procesor je ohraničen čárkovanou čarou. Jeho jediný výstup je adresa pro paměť, ze které čte instrukce. Tato adresa je uložena v registru PC (Program Counter). Nejdůležitějším registrem je Akumulátor (ACC), do kterého se zapisují výsledky operací ALU, a do kterého také můžeme zapsat přímou hodnotu pomocí instrukce. Z akumulátoru také můžeme zapisovat hodnoty do registrů v registrovém poli R. Jeden vstup ALU je vždy akumulátor, druhý je jeden z registrů.

Control nastavuje řídící signály pro ostatní prvky procesoru. Abychom mohli tento prvek navrhnout, musíme znát formát instrukce. Pro příklad zvolme velmi jednoduchý formát, kde instrukce bude mít 16 bitů, přičemž horních 8 bitů bude případný přímý operand a spodních 8 bitů budou zakódované řídící signály:

| DIRECT OPERAND | RSRVD | reg | alu | op | |15 |14 |13 |12 |11 |10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Op určuje operaci. Zvolme 4 možné operace:

00 bude zápis do PC (změna adresy pro čtení z paměti, takže instrukce skoku).01 pro provedení operace ALU.10 pro zápis přímého operandu do akumulátoru.11 pro zápis z akumulátoru do registru.Alu označuje dva bity, které určují, jaká operace ALU se má provést. Dva bity reg vybírají registr, se kterým se má provést daná operace. Další dva bity jsou prozatím nevyužité. Následuje osmibitový přímý operand.

Podívejme se tedy konečně na VHDL kód, který popisuje tento procesor. Protože entity ALU a pole registrů jsme již navrhli v předchozích dílech, vložíme je do naší entity jako tzv. komponenty. Tento přístup nám umožňuje hierarchicky skládat obvod z dílčích entit. Komponentu nejdříve musíme nadeklarovat v deklarační části architektury a v těle architektury potom provést napojení této komponenty na naše signály.

library IEEE;

use IEEE.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

ENTITY main IS

PORT (

CLK : in std_logic;

RESET : in std_logic;

INST : in std_logic_vector(15 downto 0);

ADDR : out std_logic_vector(7 downto 0)

);

END main;

ARCHITECTURE behavioral OF main IS

component ALU IS PORT (

I1, I2: IN std_logic_vector(7 downto 0);

A: in std_logic_vector(1 downto 0);

O: out std_logic_vector(7 downto 0));

END component;

component register_set IS PORT (

CLK, RESET: in std_logic;

I: in std_logic_vector(7 downto 0);

O: out std_logic_vector(7 downto 0);

ADDR: in std_logic_vector(1 downto 0);

WR: in std_logic);

END component;

signal acc, alu_acc, reg_alu: std_logic_vector(7 downto 0);

signal pc: std_logic_vector(7 downto 0);

signal op_pc, op_alu, op_reg, op_acc: std_logic;

BEGIN

p_pc: process (RESET, CLK)

begin

if (RESET = '1') then

pc <= (others => '0');

elsif (CLK'event and CLK = '1') then

if op_pc = '1' then

pc <= INST(15 downto 8);

else

pc <= pc + '1';

end if;

end if;

end process;

p_acc: process (RESET, CLK)

begin

if (RESET = '1') then

acc <= (others => '0');

elsif (CLK'event and CLK = '1') then

if op_acc = '1' then

acc <= INST(15 downto 8);

elsif op_alu = '1' then

acc <= alu_acc;

end if;

end if;

end process;

op_pc <= '1' when INST(1 downto 0) = "00" else '0';

op_alu <= '1' when INST(1 downto 0) = "01" else '0';

op_acc <= '1' when INST(1 downto 0) = "10" else '0';

op_reg <= '1' when INST(1 downto 0) = "11" else '0';

reg1: register_set port map (CLK => clk, RESET => reset, I => acc, O => reg_alu,

ADDR => INST(5 downto 4), WR => op_reg);

alu1: alu port map (I1 => acc, I2 => reg_alu, A => INST(3 downto 2), O => alu_acc);

ADDR <= pc;

END behavioral;

Vstupy naší entity jsou hodinový vstup, reset a data z paměti (instrukce). Jediným výstupem je adresa paměti.

Po deklaraci komponent a signálů následuje vlastní kód, který tvoří obvod. V něm jsou dva procesy reagující na hodinový signál, které tvoří dva registry našeho obvodu - PC a ACC. Co a zda do těchto registrů zapisovat, se řídí signály op_..., které jsou tvořeny pomocí instrukce when z dvou bitů instrukce určujících operaci procesoru. Následuje již pouze propojení komponent s registry a s ALU. K jejich řízení využíváme jednotlivé bity instrukce (např. operace ALU je dána bity 2 a 3). Spojení mezi těmito komponentami navzájem a spojení s dalšími prvky procesoru zajištují interní signály (např. z ALU do akumulátoru je to signál alu_acc).

Jako příklad funkce jsem zvolil jednoduchý program, který uloží do akumulátoru hodnotu 1, tuto hodnotu zapíše do registru R1 (přímý zápis do tohoto registru není možný), uloží do akumulátoru hodnotu 3, inkrementuje tuto hodnotu a poté provede skok opět na tuto instrukci inkrementace. Simulace běhu tohoto programu je zde:

Vícebitové hodnoty jsou zobrazeny v hexadecimálním formátu. Pokud chcete vidět přesnou funkci tohoto programu, je třeba převést hodnoty instrukce do binárního formátu a porovnat s formátem instrukce.

V signálu Addr je zřejmé, že Program Counter na adrese 04 narazil na instrukci skoku na adresu 03, čímž se vytvořila nekonečná smyčka. V registru Acc (akumulátor) můžeme vidět inkrementující se hodnotu. První operace je zápis do akumulátoru (aktivní signál op_acc), poté zápis akumulátoru do registru (signál op_reg) a znovu zápis do akumulátoru. Potom již jen inkrementujeme akumulátor v nekonečné smyčce.

Procesor, který byl zvolen pro ilustraci, má řadu nedostatků, např. neumožňuje podmíněné skoky, formát instrukce plýtvá pamětí atd. Řešení těchto nedostatků však může posloužit jako cvičení zvídavému čtenáři.

Tímto náš úvod do VHDL končí. Cílem bylo ukázat, že hardware je možné popsat pomocí jazyka. Pokud ve vás alespoň trošku vzbudil zájem o problematiku návrhu obvodů, potom splnil svůj účel. Všem děkuji za pozornost!

Nástroje: Tisk bez diskuse

Tiskni

Sdílej:

![]()

![]()

![]()

![]()

![]()

![]()

, na východě se používá oboje, v Evropě zase spíše VHDL... takže tak jednoznačné to není. Jinak Verilog má možná open source simulátor, nicméně samotný je propietární a zatížen licencováním, zatímco VHDL je otevřený standard. Existují pro něj jak open source simulátory, tak také komplet simulátor -- syntezátor -- router. Verilog je sice jednodušší, o to je zas ale VHDL komplexnější. Na návrh procesorů, případně architektur se také nemusí použít ani jedno, ale můžeš vycházet třeba z IDL či ADL.

Jinak není to jedno kdo co používá? Není trolovatění se proč každý nepoužívá ten můj nejoblíbenější super tuper jazyk dětinské?

, na východě se používá oboje, v Evropě zase spíše VHDL... takže tak jednoznačné to není. Jinak Verilog má možná open source simulátor, nicméně samotný je propietární a zatížen licencováním, zatímco VHDL je otevřený standard. Existují pro něj jak open source simulátory, tak také komplet simulátor -- syntezátor -- router. Verilog je sice jednodušší, o to je zas ale VHDL komplexnější. Na návrh procesorů, případně architektur se také nemusí použít ani jedno, ale můžeš vycházet třeba z IDL či ADL.

Jinak není to jedno kdo co používá? Není trolovatění se proč každý nepoužívá ten můj nejoblíbenější super tuper jazyk dětinské?