Ve FreeBSD byla nalezena a již opravena 21letá zranitelnost CVE-2026-42511 v dhclient. Jedná se o vzdálené spuštění kódu (RCE). Útočník mající pod správou DHCP server může získat plnou kontrolu nad systémem FreeBSD pouze jeho připojením k místní síti.

Na čem aktuálně pracují vývojáři GNOME a KDE Plasma? Pravidelný přehled novinek v Týden v GNOME a Týden v KDE Plasma.

UBports, nadace a komunita kolem Ubuntu pro telefony a tablety Ubuntu Touch, vydala Ubuntu Touch 24.04-1.3. Současně oznámila, že nadcházející větší vydání 24.04-2.0 bude mít modernější webový prohlížeč.

Ploopy po DIY trackballech či sluchátkách představuje nový externí DIY trackpoint se čtyřmi tlačítky Bean. Obsahuje snímač Texas Instruments TMAG5273, spínače Omron D2LS-21 a řadič RP2040, používá firmware QMK. Schémata jsou na GitHubu; sadu lze předobjednat za 69 kanadských dolarů (bez dopravy a DPH).

Mozilla před dvěma týdny na svém blogu oznámila, že díky Claude Mythos Preview bylo ve Firefoxu nalezeno a opraveno 271 bezpečnostních chyb. Včera vyšel na Mozilla Hacks článek s podrobnějšími informacemi. Z 271 bezpečnostních chyb mělo 180 chyb vysokou závažnost, 80 chyb střední závažnost a 11 chyb nízkou závažnost. Celkově bylo v dubnu ve Firefoxu opraveno 423 bezpečnostních chyb. Čísla CVE nemusí být přiřazována jednotlivým chybám. CVE-2026-6784 například představuje 154 bezpečnostních chyb.

Před týdnem zranitelnost Copy Fail. Dnes zranitelnost Dirty Frag. Běžný uživatel může na Linuxu získat práva roota (lokální eskalaci práv). Na většině linuxových distribucí vydaných od roku 2017. Aktuálně bez oficiální záplaty a CVE čísla [oss-security mailing list].

Ačkoli je papež Lev XIV. hlavou katolické církve a stojí v čele více než miliardy věřících po celém světě, také on někdy řeší všední potíže. A kdo v životě neměl problémy se zákaznickou linkou? Krátce poté, co nastoupil do úřadu, musel papež se svou bankou řešit změnu údajů. Operátorka ale nechtěla uvěřit, s kým mluví, a Svatému otci zavěsila.

Incus, komunitní fork nástroje pro správu kontejnerů LXD, byl vydán ve verzi 7.0 LTS (YouTube). Stejně tak související LXC a LXCFS.

Google Chrome 148 byl prohlášen za stabilní. Nejnovější stabilní verze 148.0.7778.96 přináší řadu novinek z hlediska uživatelů i vývojářů. Vypíchnout lze Prompt API (demo) pro přímý přístup k AI v zařízení. Podrobný přehled v poznámkách k vydání. Opraveno bylo 127 bezpečnostních chyb. Vylepšeny byly také nástroje pro vývojáře.

Richard Hughes oznámil, že po společnostech Red Hat a Framework a organizacích OSFF a Linux Foundation, službu Linux Vendor Firmware Service (LVFS) umožňující aktualizovat firmware zařízení na počítačích s Linuxem, nově sponzorují také společnosti Dell a Lenovo. Do dnešního dne bylo díky LVFS provedeno více než 145 milionů aktualizací firmwarů od více než 100 různých výrobců na milionech linuxových zařízení.

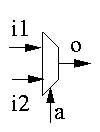

Syntaxi příkazu when si ukážeme na následujícím

příkladu:

O <= I1 when A = '0' else I2;

Tento zápis znamená: do signálu O přiřaď signál

I1, pokud je hodnota signálu A '0', jinak do

signálu O přiřaď signál I2. Důležité je uvědomit

si, že tímto příkazem neříkáme, co chceme vytvořit, ale jak se má výsledný

obvod chovat. Z tohoto zápisu dostaneme zřejmě multiplexor,

obvod, který funguje jako přepínač. Tento konkrétní multiplexor přepíná

vstupy I1 nebo I2 na výstup O podle

jednobitové adresy A.

Nyní můžeme pomalu začít skládat náš procesor. Uvažujme osmibitovou

architekturu, šířka datových sběrnic tedy bude osm bitů. Pracovat s

jednotlivými vodiči (signál std_logic) by bylo zdlouhavé,

využijeme proto typ signálu std_logic_vector, který vzniká

složením jednotlivých signálů std_logic. Při deklaraci

signálu std_logic_vector určujeme pořadí bitů - např. (7

downto 0) znamená osmibitový signál s nejméně významným bitem vpravo, s

bity číslovanými od 0 do 7. Konstanty typu std_logic_vector

se zapisují v uvozovkách (např. "1010").

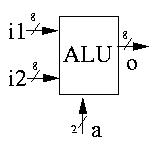

Jako první prvek vytvoříme ALU - aritmeticko-logickou

jednotku. V procesoru zajišťuje realizaci aritmetických a logických

funkcí.

Do naší ALU vedou dva osmibitové datové vstupy

I1 a I2, výsledek operace je přiveden na výstup

O. Operaci (zvolme např. AND, OR, NOT, +) určujeme

dvoubitovým signálem A (dva bity jsou dostatečné k adresování

právě jedné ze čtyř operací).

library IEEE;

use IEEE.std_logic_1164.all;

use ieee.std_logic_arith.all; -- vlozeni potrebnych knih.

use ieee.std_logic_unsigned.all;

ENTITY ALU IS

PORT (

I1, I2: IN std_logic_vector(7 downto 0); -- dva 8bitove datove vstupy

A: in std_logic_vector(1 downto 0); -- 2bitova adresa operace

O: out std_logic_vector(7 downto 0) -- jeden 8bitovy vystup

);

END ALU;

ARCHITECTURE behavioral OF ALU IS -- tvorime obsah entity ALU

BEGIN

O <= I1 AND I2 when A = "00" else -- na vystupu logicky soucin

I1 OR I2 when A = "01" else -- logicky soucet

not I1 when A = "10" else -- negace I1

I1 + I2; -- scitani

END behavioral;

V deklaraci entity definujeme vstupy a výstupy ALU. Tělo architektury

se skládá z jediného příkazu when, který určuje, jaká funkce

se má objevit na výstupu při různých kombinacích bitů adresy. Fyzická

realizace této funkce by odpovídala čtyřem obvodům realizujících dané

funkce (AND, OR, NOT, +) a čtyřvstupového osmibitového multiplexoru, který

vybírá výsledek jednoho z obvodů na výstup dle hodnoty signálu A.

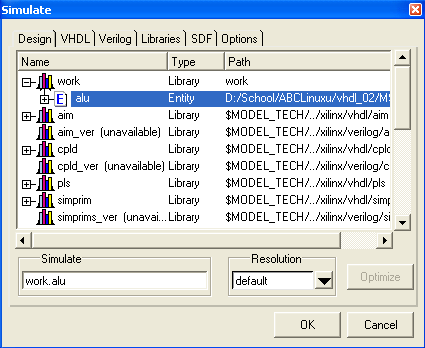

Co dál s VHDL kódem? V úvahu připadají dvě činnosti

simulace nebosyntézaSimulace je ověření činnosti obvodu na počítači - program (simulátor) napodobuje činnost obvodu a v podobě časového průběhu signálů je možné sledovat funkci obvodu. Syntéza je převod VHDL kódu do formátu vhodného pro fyzickou realizaci obvodu.

Nyní si řekněme něco více o simulaci. Odsimulovat kód si můžete zkusit sami na domácím počítači, např. pomocí volně šiřitelného software ModelSim XE Starter, který si můžete stáhnout ze stránek firmy Xilinx. Program vyžaduje jednorázovou registraci. Po stáhnutí a nainstalování je ještě třeba požádat o registrační klíč přes internetový formulář.

Po spuštění programu je nejdříve potřeba vytvořit nový projekt (File -> New -> Project). Poté si buď vytvoříte nový soubor pro zápis VHDL kódu (např. pravé tlačítko myši v prostoru Workspace -> Add to Project -> New File), nebo přidáte do projektu již existující soubor (pravé tlačítko -> Add to Project -> Existing File). V našem případě bude soubor obsahovat kód ALU uvedený výše.

Příkazem Compile -> Compile All zkompilujete zdrojové soubory do knihovny work. Nyní je možné spustit režim simulace pomocí Simulate -> Simulate. Vybereme entitu ALU z knihovny Work (je třeba rozvinout záložku work).

V hlavním okně ModelSimu se nyní objevila nová záložka sim, pomocí které můžeme nastavovat entitu, se kterou chceme pracovat (v našem případě je to pouze ALU). Z menu View nyní můžeme vyvolávat okna potřebná pro simulaci, nejdůležitější jsou okna Signals a Wave. Wave zobrazí časový průběh signálů (prozatím je prázdné). V okně Signals vidíme všechny signály použité v entitě (včetně portů), které můžeme přidat do okna Wave (Add -> Wave -> Signals in Region).

Jsme sice v režimu simulace, ale zatím jsme nic neodsimulovali. Simulaci musíme nechat běžet po určitou dobu - to můžeme udělat např. v hlavním okně ModelSimu v příkazovém řádku pomocí příkazu run s parametrem času, po který má simulace běžet. Pokud chceme např. simulovat obvod po dobu 100 nanosekund, zadáme příkaz run 100 ns.

Pokud jste celý postup provedli na příkladu naší ALU, objevily se vám v okně Wave na časové ose červené čáry.

Tím nám simulátor říká, že hodnoty signálů nejsou definované. Musíme proto na vstupy obvodu nastavit úrovně signálů - v okně Signals vybereme signál, do kterého chceme vnutit hodnotu a v Edit -> Force -> Value zadáme binárně hodnotu. Pokud např. zadáme hodnoty I1 10101010, I2 00001111, A 00 (funkce logického součinu) a znovu spustíme simulaci (run 100 ns), na výstupu O se nám objeví hodnota 00001010 (logický součin vstupů I1 a I2). Pokud je vidět pouze konec simulace, je dobré zobrazit celý průběh v okně Wave - View -> Zoom -> Zoom Full.

Nyní si můžete hrát s různým nastavováním signálů a testování funkce

ALU. Postup přímého zadávání hodnot signálů je velmi zdlouhavý, v praxi se

používá spíše metoda nadřazené entity zvané testbench , o

kterém budeme hovořit v některém z dalších dílů.

Obvod máme odsimulovaný, dalším krokem v průběhu návrhu je syntéza. Pro syntézu již potřebujete další hardware, běžně se používají programovatelná hradlová pole CPLD nebo FPGA. Dostupné jsou i hotové kity, které řeší napájení programovatelného obvodu a jeho připojení k PC a periferiím. Pokud zvolíte obvod CPLD nebo FPGA firmy Xilinx, můžete si k nim zdarma stáhnout nástroj pro syntézu ISE WebPack. S tímto vybavením si můžete sami obvod nahrát a používat.

Důležité při psaní VHDL kódu je uvědomit si, co vlastně děláme. Nepíšeme program, ale určujeme funkci obvodu. Z toho také vyplývá použití programovatelných polí - hodí se pro paralelní nebo časově kritické aplikace, pro implementaci složitých algoritmů je naopak lepší využít procesor.

Nástroje: Tisk bez diskuse

Tiskni

Sdílej:

![]()

![]()

![]()

![]()

![]()

![]()

) nemaji zpetne vazby v logice co delat - v kazde zpetne vazbe musi byt v ceste registr.

) nemaji zpetne vazby v logice co delat - v kazde zpetne vazbe musi byt v ceste registr.